# Propelling AI forward through Advanced Packaging Creativity

Calvin Cheung ASE, Inc.

GSA Tech Summit July 1 2025

aseglobal.com

### **AI IS HERE**

- Al applications permeating global life, creating new efficiencies and new markets, from data center to edge devices.

- Al economy projected to soar from \$189 billion in 2023 to \$4.8 trillion by 2033 a 25-fold increase in just a decade

- Al adoption could boost global GDP by 15% by 2035, based on game-changing capabilities and safe deployment.

- Unprecedented data generation is driving global datasphere trajectory towards 200ZB by 2030

<sup>2</sup> Source: UN Trade and Development (UNCTAD), PwC, IDC 2025

### Semiconductor industry scaling

The AI innovation ecosystem is driving the global semiconductor market with demand for:

- New equipment

- New materials

- New architecture

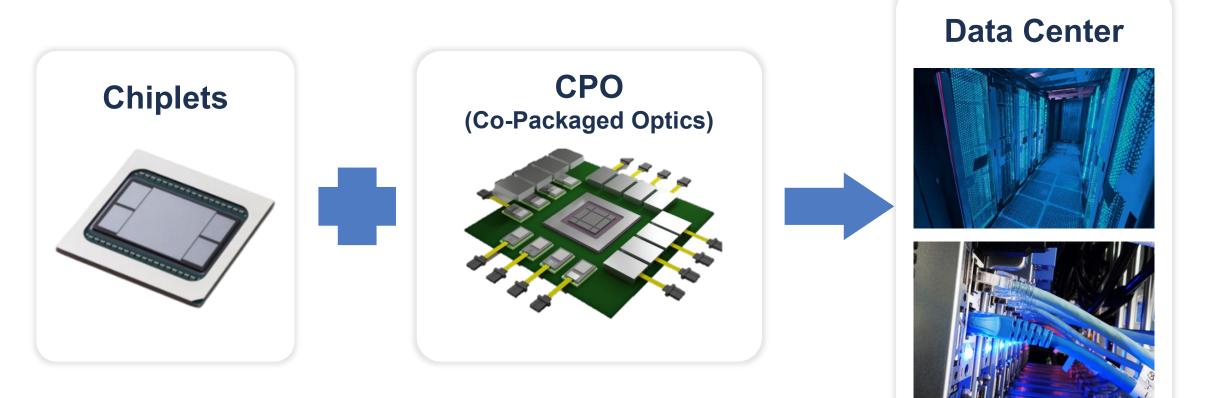

#### Advanced Packaging is bringing transformative innovation to address critical thermal and electrical challenges

- Heterogenous integrated solutions

- Power management devices

- Co-Packaged Optics

3

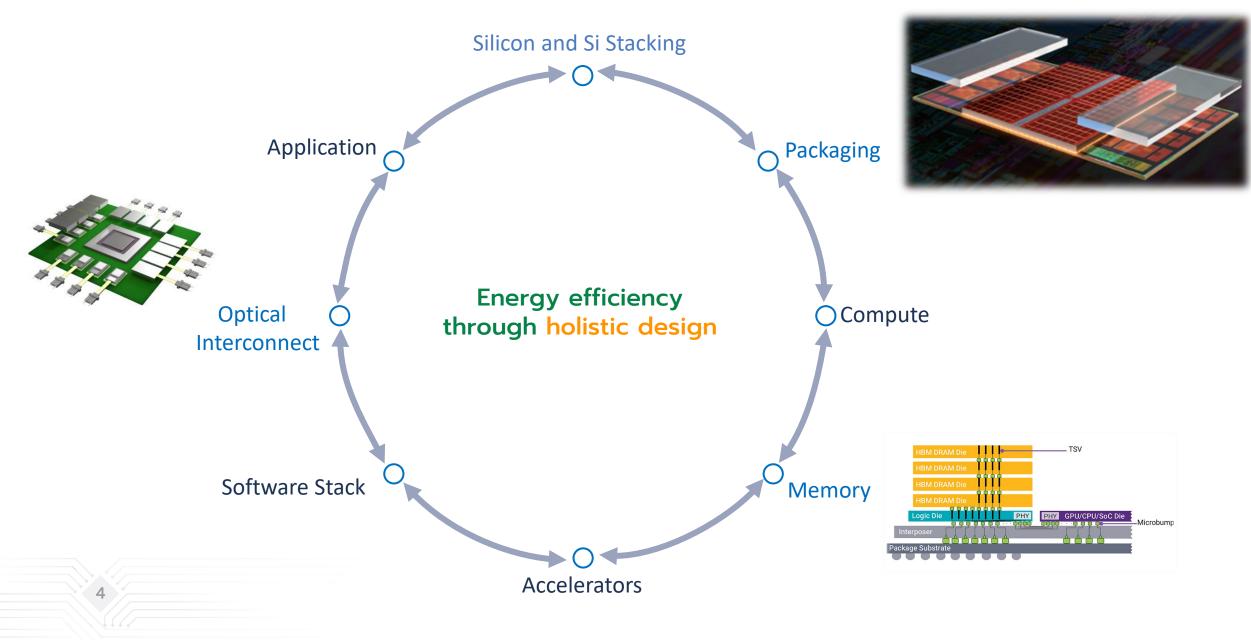

#### Advanced Packaging Delivers Holistic System Level Efficiency

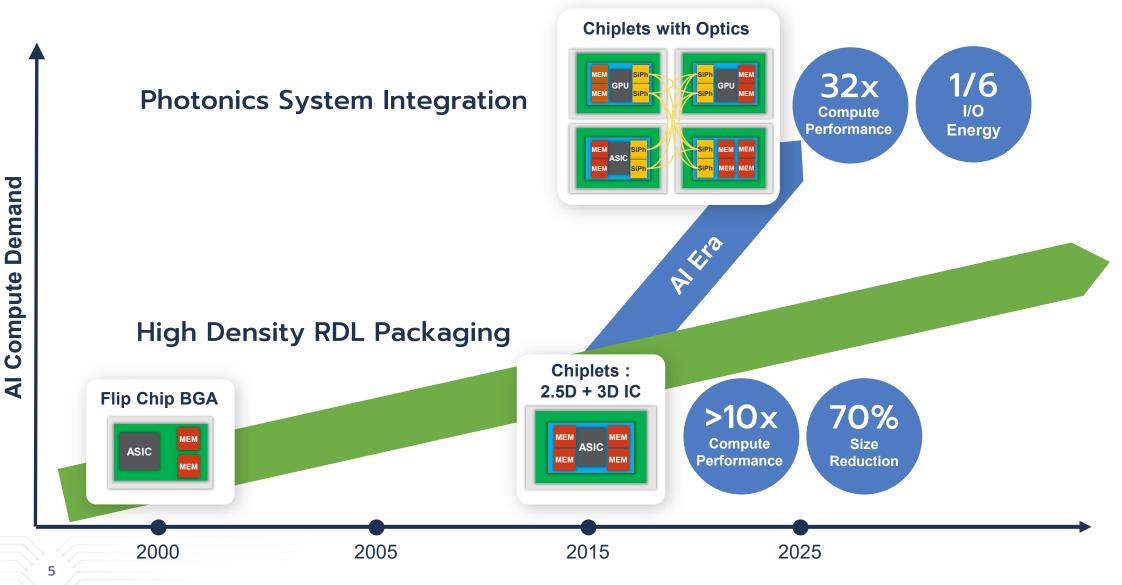

## Packaging evolution for AI systems

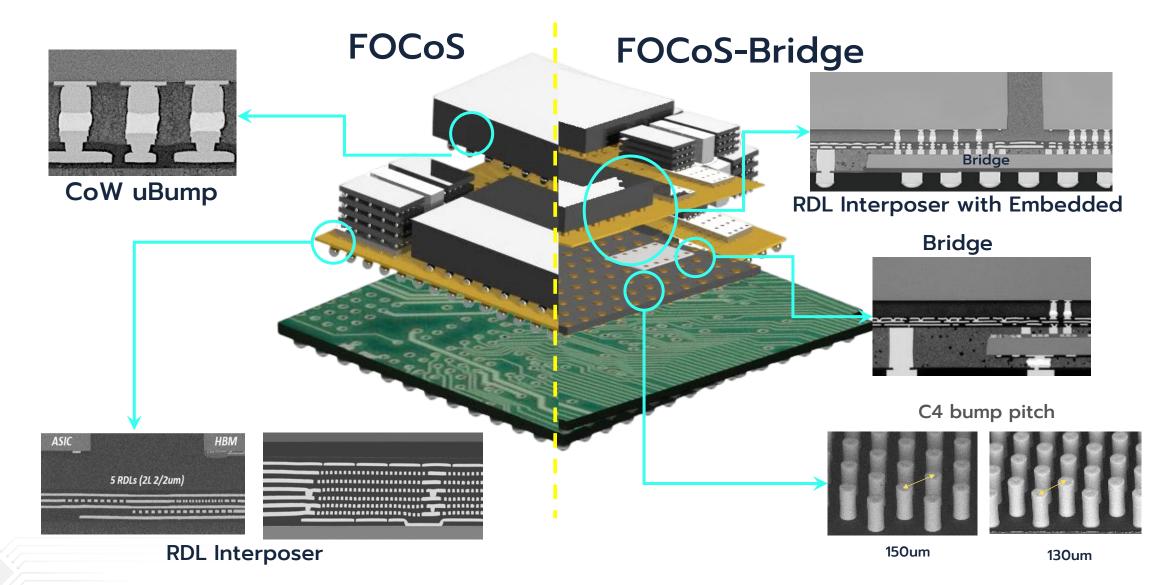

### Exploring FOCoS & FOCoS-Bridge

6

### **Panel utilization**

#### Panel Utilization vs. Reticle Size 600mm Panel 300mm Wafer 300mm Panel 100% -% Avg: 90% -**Utilization Rate** Avg: 70% 80% 70% -Avg: 57% 60% 50% -Reticle Size 1x **2**x 3x **4**x **5**x 1x 2x 3x 5x 1x **2**x 3x **5**x **4**x **4**x

7

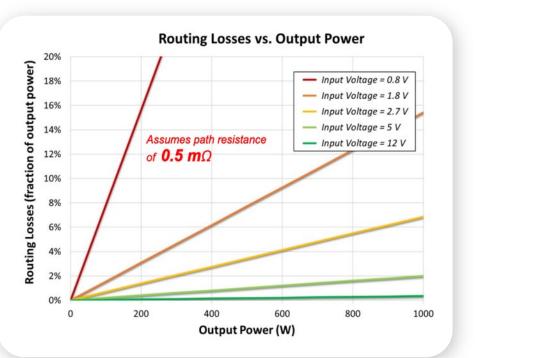

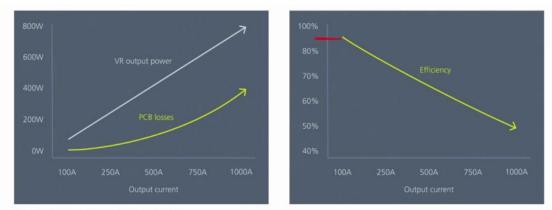

### The need for IVR/VRM

High power at lower voltages requires high current and causes high power delivery loss (I<sup>2</sup>R) – Power

delivery needs to be in short distance = vertical power delivery

#### Escalating need to integrate power conversion from high voltage at point of load (PoL)

- integrate new power delivery architectures = Vertical power delivery

Source: 2024 IEEE VLSI Symposium on Technology & Circuit

8

Example with PCB resistance of  $400\mu\Omega$  (VR at  $0.8V_{OUT}$ )

|                      | Vicor Lateral                  | Conventional           |

|----------------------|--------------------------------|------------------------|

| PDN resistance       | 50μΩ                           | 400μΩ                  |

| PDN loss @ 500 Amps  | 12.5W loss<br>96.8% efficiency | 100W<br>75% efficiency |

| PDN loss @ 1000 Amps | 50W loss<br>93.75% efficiency  | 400W<br>50% efficiency |

PDN Power Loss, due to circuit board copper resistance = I<sup>2</sup>R

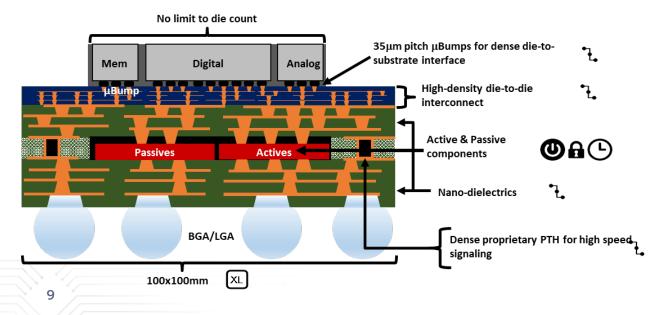

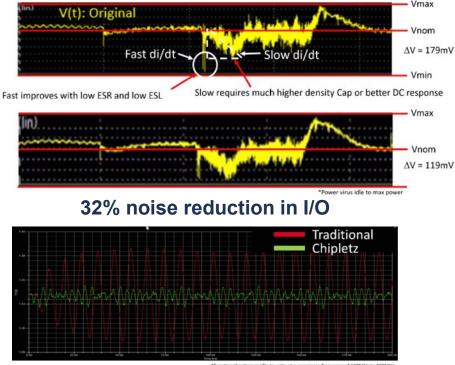

#### Power delivery innovation: Voltage Regulator Module

- PIM's cost & performance are better than after 7nm advanced node develop

- Decoupling frequency 100MHz → 200MHz:

- Clock & PHY VDD I/O 32% noise reduction

- Driver VDD 78% noise reduction

- Voltage drop 179mV → 119mV, 60mV improve could increase ~40% frequency

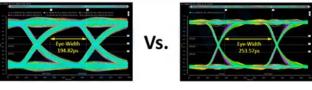

- Fast die-to-die interconnect and lower power via 30% wider eye

#### **Better HBM Signaling**

Silicon interposer

#### Organic substrate

#### 32% noise reduction

Functional pattern is idle to write at a resonance frequency of 100MHz to 200MH.

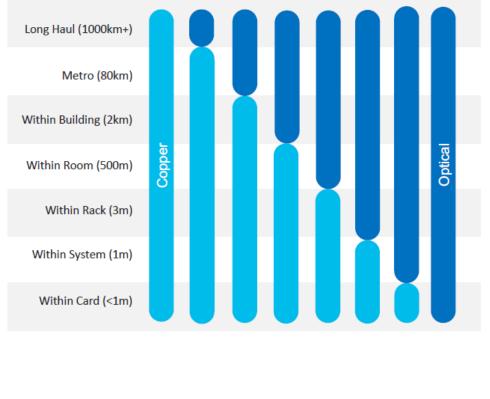

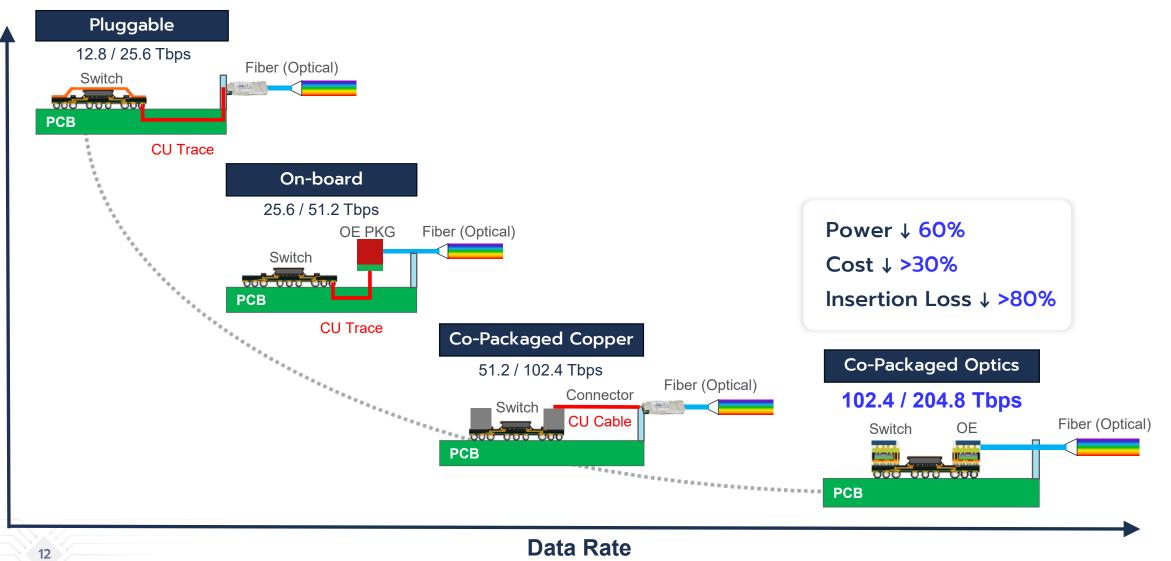

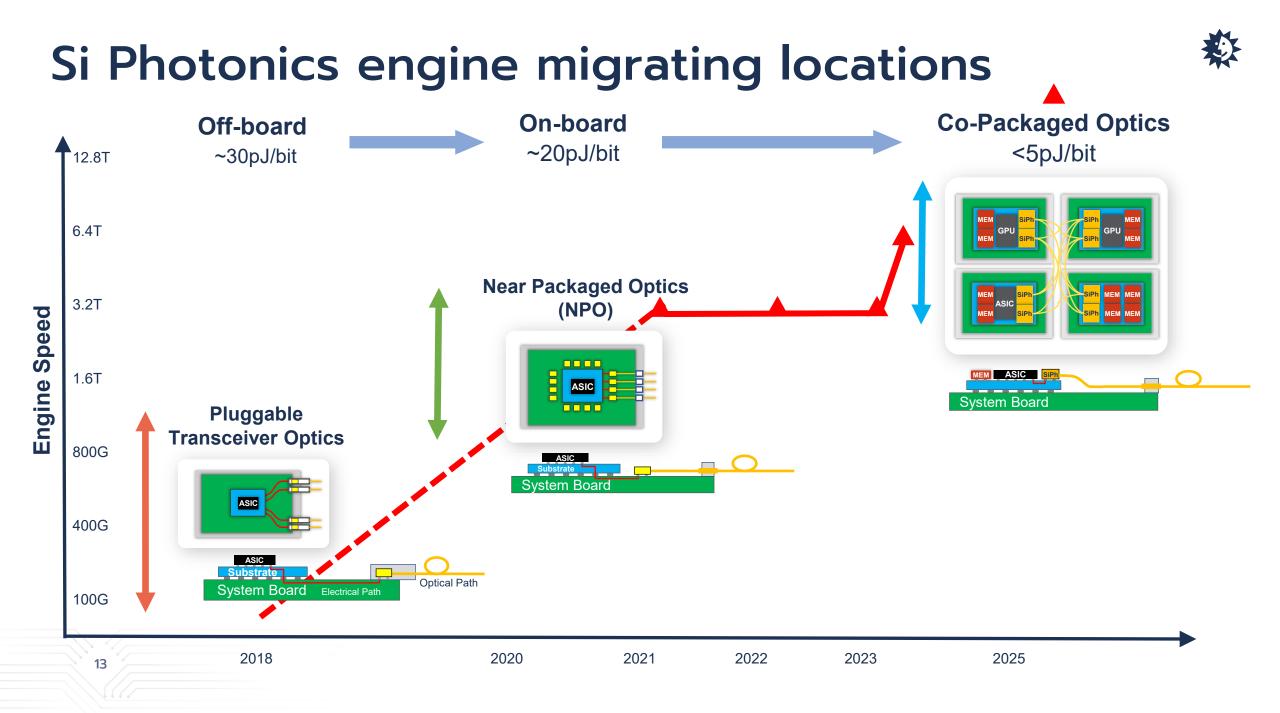

### The future is optical

Future system capacity will only be possible with Silicon & Optical Integration

Time & Speed

### **Heterogeneous Integration: Silicon Photonics**

#### Power Efficiency through Silicon Photonics

#### **CPO System - Supply Chain Ecosystem** System Requirement Data Center Architect **ODM - OEM** System Integration **New Generation ODM-OEM Optical Requirement** Chip Design Foundry **OSAT/EMS OSAT/EMS OSAT PIC/EIC** Module/OBO/CPO Chip MFG **EIC/PIC** Optics ASSY & Test Integration ASSY & Test

### Summary

Al and Data continue to fuel semiconductor innovation, with exponential proliferation through 2030 and beyond that will shape global life and lifestyle in unimaginable ways.

Collectively, our industry is accelerating the Al economy through Heterogeneous Integration advancements.

Packaging creativity is enabling seamless integration of multiple chiplets, SiPs, modules into one single package optimized for enhanced functionality and operating characteristics.

# Thank you