# Leveraging Al to Optimize DFT and Test Implementations

Isabel Camaclang

MTS Silicon Design Engineer

## **Outline**

- Introduction

- Motivation

- Design-for-test (DFT) challenges

- Scan architecture optimizations and DFT assistants

- Conclusion

#### Introduction

- Design-for-test (DFT)

- A discipline in silicon design focused on techniques assuring integrated circuits are testable

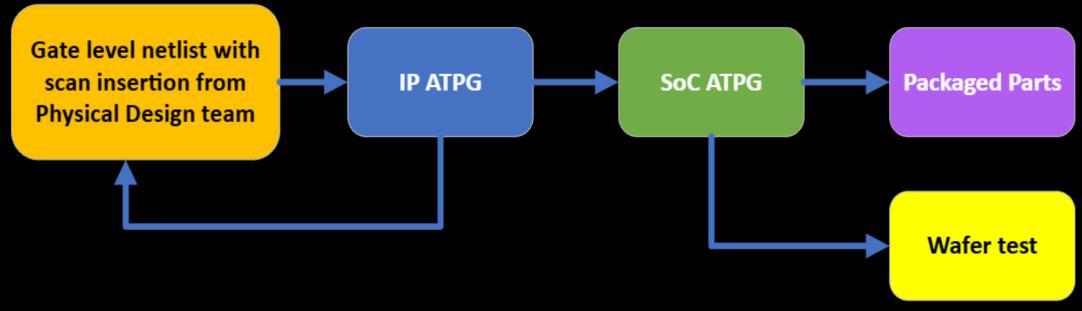

- Automatic Test Pattern Generation (ATPG)

- Generate patterns to detect modeled manufacturing defects

- Defect parts per million (DPPM)

- The lower the better

#### Introduction

- Machine-learning

- Allows for the development of algorithms that can learn from data to perform tasks requested by users

- Utilizes predictive analytics, natural language processing, and speech recognition

- Confidence score

- Large Language Model (LLM)

#### **Motivation**

- Save iteration time in defining and implementing optimized scan structure

- The need for lower pattern count and high-test coverage

- Bug and information broadcasting or distribution

# **DFT challenges**

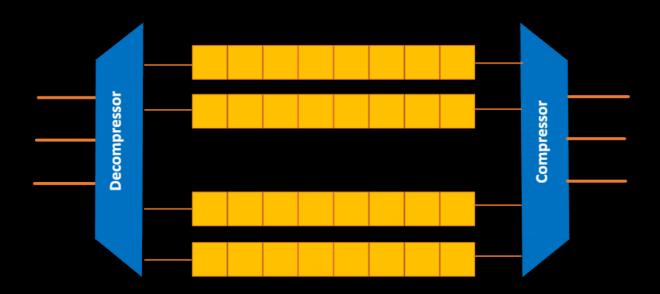

- Optimized compression ratio

- Optimized scan chain channel distribution

- Optimized scan chain length

# **DFT** challenges

- Not easily accessible or understanding of DFT and ATPG learnings, information, and documentations

- Overwhelming volume of irrelevant data when searching for specific topic, issues or solutions

- Time consuming iteration of ATPG run to find optimized scan compression and architecture

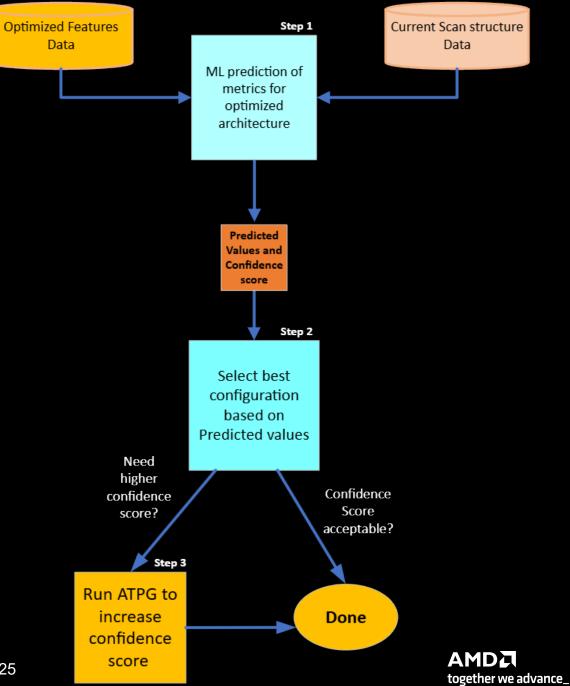

### Scan architecture optimization

- Input data:

- Optimized features

- Current design scan structure

- ML Prediction

- Select best configuration

- Check confidence score

- Accept or Run ATPG to increase confidence score

#### **Virtual assistants**

- Can use utilized by DFT verification, design and structural engineers

- DFT verification debug helper collect verification logs to streamline debug process

- DFT chatbot trained with DFT related documents, learnings, bugs. Utilize learning abilities to differentiate relevant from irrelevant information

#### **Benefits**

- Expected benefits are lower pattern count, higher test coverage, optimized compression ratio

- DFT assistants can support engineers to increase productivity

- DFT assistants can also help in distributing information

#### Conclusions

- ML engine to improve scan designs and structures

- All assistants to help DFT engineer productivity

- Optimized scan structure with less ATPG iterations

# Acknowledgements

We would like to thank the following AMD-ers for their support:

Noah Marra Sergey Miroshnikov Eric Chan Bikash Agarwal Tassanee Payakapan Arie Margulis Rahul Malhotra Dhivyamai Thoppay-s Monica Farkash Khushboo Agarwal Ahmet Tokuz Jeff Rearick

# Thank you

#### Copyright and disclaimer

©2025 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions, and typographical errors. The information contained herein is subject to change and may be rendered inaccurate releases, for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. Any computer system has risks of security vulnerabilities that cannot be completely prevented or mitigated. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

THIS INFORMATION IS PROVIDED 'AS IS." AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS, OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION. AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY RELIANCE, DIRECT, INDIRECT, SPECIAL, OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION

#