27 APR 2023

Can I own my AI?

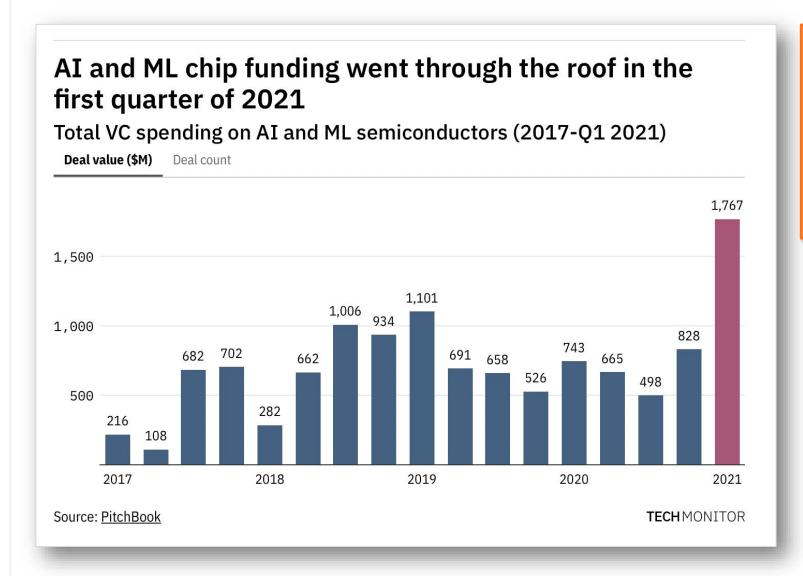

## Al semiconductor clearly sees a strong momentum

Al chip technology is evolving rapidly, Gartner estimates that more than 50 companies are making chips specifically for Al, and Al-specific chip revenue is expected to reach \$76.8 billion by 2025

## Let's look at several key trends for AI SoCs

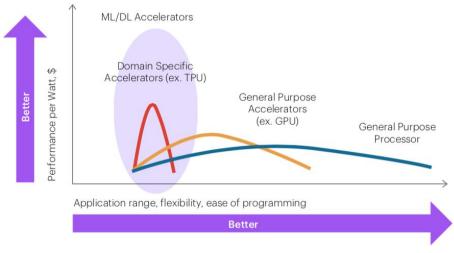

- Accelerator-based designs: <u>Domain Specific</u> IP for training and inference work <u>more efficiently</u> than general-purpose CPUs and GPUs.

- Al at the Edge: Growing trend towards processing Al workloads at the edge prioritize low-power and smaller die size

- Memory Architecture: Reduced Latency is the holy grail in Al workloads. Chip designs are increasingly focused on optimizing memory architecture/choices

- Hybrid architectures: Migration of AI chips using combination of different types of accelerators to optimize performance for specific AI workloads – chiplet opportunity

- Increasing performance: Demand for performance of AI chips (training), both in terms of die size, raw compute power and energy efficiency are driving innovation in chip design, materials science, and cooling technology.

Source: GSA AI whitepaper, Dell

#### Choosing the Correct Memory: Comparison Data

| Parameter                     | LPDDR4x             | LPDDR5            | DDR4                | GDDR6              | НВМ2Е            |

|-------------------------------|---------------------|-------------------|---------------------|--------------------|------------------|

| Bandwidth (Gbps)              | Low-Medium<br>(136) | Medium<br>(204)   | Medium (200)        | High (512)         | Highest (3686)   |

| Data Rate (Gbps)              | 4.266               | 6.4               | 3.2                 | 16                 | 3.6              |

| Interface width (bits)        | 32                  | 32                | 64                  | 32                 | 1024             |

| Board Area / System<br>Design | Large / Medium      | Medium/<br>Medium | Large / Easy        | Medium /<br>Medium | Small / Complex  |

| Efficiency (mW/Gbps)          | High (3)            | High (3)          | Moderate (10)       | Moderate (10)      | Highest (2)      |

| Cost (\$)                     | Medium              | Medium            | Low                 | Medium             | High             |

| Reliability/Yield             | Good                | Good              | Good                | Good               | Moderate         |

| Applications                  | Mobile, Al          | Mobile, Al        | Compute,<br>Network | AI, Graphics, Auto | AI, HPC, Network |

Source: Rambus

## The AI Chip Revolution has begun.....

More effort and partnership collaboration is required to realize IDEAS and INNOVATION into Silicon

## So...Can I OWN my AI?

Cost of designing custom silicon is too prohibitive

\$\$\$ - EDA tools, IP licenses, people.....

cost my Al

I need to have my silicon in months and not years

Too much risks – unproven IP new design flows etc

I don't have the right team

Combletic

It's just too hard!

Multi touch points (EDA, IP, Foundry, OSATs etc...)

We need to get more specialized chips

... but we cannot!

No way I can risk **\$20M upfront** and **spend 2 years**before I get the first MVP!

\$20M+

Design NRE

\$10M

Upfront IP

License

\$5M

Fab cost \$5M

**Upfront cost**

on Chip Owner on Design House **Application Specs** Physical Implementation Physical Design **Custom Domain IP** SoC Specs PKG Architecture **Key IP Configuration Verification Requirements** HW/SW Bring-up **Duplicated Efforts**

Dependency

Is there opportunity to reduce duplicated efforts?

Need to Dramatically Enhance Design Reusability in Chip Design

## on Chip Owner

**Application Specs**

**Custom Domain IP**

Unique Value

Reusable Efforts

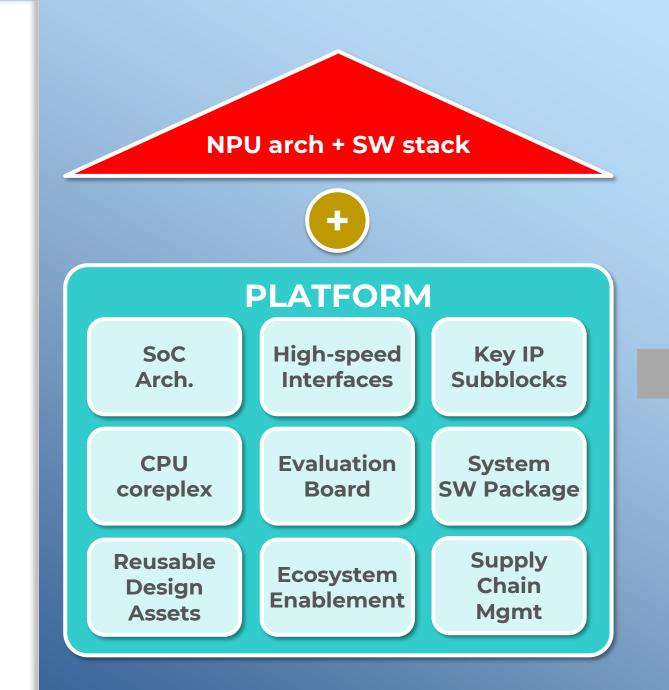

## on Design Platform

SoC Specs

Architecture

**Key IP Configuration**

**Verification Requirements**

HW/SW Bring-up

Physical Implementation

**Physical Design**

PKG

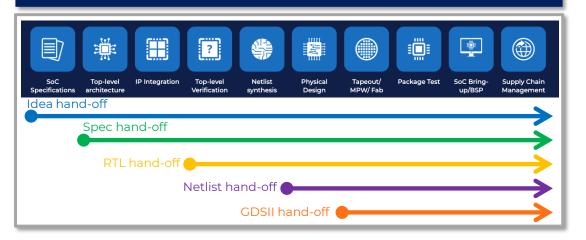

Platform-based Al Chip Development

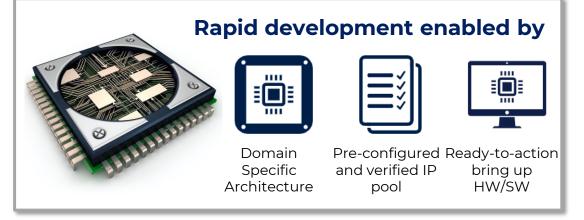

### Our answer: Platform-based Al solution

#### **Lower Development Cost**

- Up to 50%+ lower\* (vs industry average)

- Cost reduction for design NRE, Fabrication & IP licenses

#### Rapid Time to Market

- Up to 50%+ shorter\* than industry average

- Maximize design / verification component reusability

#### **Reduced Engineering Risk**

- Pre-verified IPs and Silicon-proven Platform

- End-to-end solution with expertise from architecture consulting to PKG/Test/SW Bring-up

# Platform

**SEMIFIVE**

Design

#### Simplest Engagement Model

- SEMIFIVE manages entire silicon design and manufacturing process (IP, EDA, Foundry, OSAT, etc)

- Customer can solely focus on their own technology/idea.

<sup>\*</sup> Case with maximum reuse of SEMIFIVE's platform SoC

## Enabling innovators & disruptors to realize differentiated AI silicon

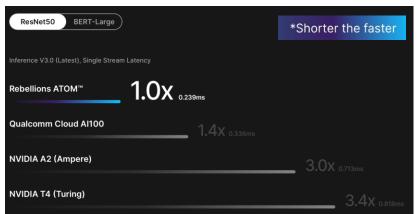

Source: Rebellions

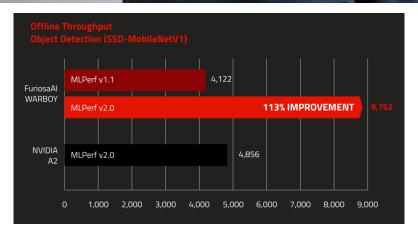

Source : FuriosaAl

Kick off to Tapeout in just

6 months!

11

## Examples: Platform-based AI chips taped out at Samsung Foundry

#### Al Inference SoC platform **HPC AI SoC platform AIoT SoC platform 14nm 14nm** 5<sub>nm</sub> CPU Peripherals System System CPU **Peripherals** CPU Peripherals System Debug/Trace OTP UART v2 OTP Debug/Trace QSPI x2 Debug/Trace U74 32KB L1CC IRQ U74 32KB U74 32KB RTC SPI x4 GPIO x96 A53 32KB LICC A53 32KB OTP A53 32KB GPIO x64 32KB LICC DMA LICC IRQ GPIO x64 LICC 12C x4 WDT WDT DMA UART x2 12C x2 2MB L2CC 2MB L2CC 512KB L2CC DMA SRAM I2C x2 WDT OSPL x2 PVT SRAM 12S x2 SRAM **Customer IP Customer IP Customer IP** PWM x2 PVT PWM x4 HCA PWM 4ch x1 PVT High ligh Performance **High Performance High Performance High Performance** High **Interleaved Memory System** Performance Interleaved Interfaces Performance Interleaved Memory System **Interface Memory System** Interface LPDDR4 LPDDR4 LPDDR4 LPDDR4 MIPI CSI eMMC SDIO LPDDR4 GDDR6 GDDR6 GDDR6 GDDR6 Controller PCIE Gen4 (8Lane) Controller Controller Controller Controller PCIE Gen5 (16Lane) I PDDD4 x32 4266 **PCIE Host** x32 4266 x32 4266 x32 4266 PCIE Host Camera Target market/application Target market/application Target market/application Data center accelerator Consumer (e.g., wearables) Hyperscale Data Centers Al Vision processor **Cloud Servers** Surveillance and Smart Security Big data analytics Smart home **Network Processors** Image/Video recognition Industrial IoT (incl smart factory) High performance AI accelerators ADAS with real time processing Robotics First pass silicon success. 2<sup>nd</sup> TO In mass production! 2 additional DWs TO completed. Engaging multiple using same platform completed in 1023 customers

## SEMIFIVE ASIC designs with other Tierls / Set / OEMs companies

| Project | Application | Samsung Foundry<br>Process node | Die Size |

|---------|-------------|---------------------------------|----------|

| А       | AI SoC      | 14nm                            | ~ 200mm² |

| В       | AI SoC      | 14nm                            | ~ 200mm² |

| С       | AI SoC      | 5nm                             | ~ 150mm² |

| D       | AI SoC      | 14nm                            | ~ 200mm² |

| Е       | AI IOT      | 14nm                            | ~ 80mm²  |

| F       | AI CV       | 8nm                             | ~ 40mm²  |

| G       | 5G Network  | 4nm                             | ~ 300mm² |

| Н       | Energy SoC  | 4nm                             | ~ 20mm²  |

#### SEMIFIVE - A little about us

#### "New Global Hub of Custom Silicon"

- ☐ Founded in 2019, completed 4 acquisitions\*

- Engineering focused with 340+ Engineers

- ☐ USD\$150M raised (up to Series B)

- ☐ Engineering team Experience 250+ tapeouts

- SEMIFIVE has 10+ T/O on adv FinFET (14/8/5nm)

- Official Samsung Foundry SAFE DSP

\* Sesol Semi, Dahsim Semi (2019), Hanatec (2021), AnalogBits (2022)

#### We are global and growing

#### Flexible end2end turnkey ASIC service

## **Unique SOC Platforms**

## Can I own my AI?

- ☐ Tremendous AI market and application opportunities

- More effort needed to address challenges in design architecture, memory optimization/options, latency, hybrid solutions etc

- ☐ We need tighter collaboration between idea creators, system innovators, chip designers, silicon providers to software teams

□ And YES! You can own your AI with SEMIFIVE

# THANK YOU

**New Global Hub of Custom Silicon**

More information can be found at our new website

www.semifive.com